ざっと各ICに電源が接続されていることが導通チェックできたので、通電して各部の確認を始めました。

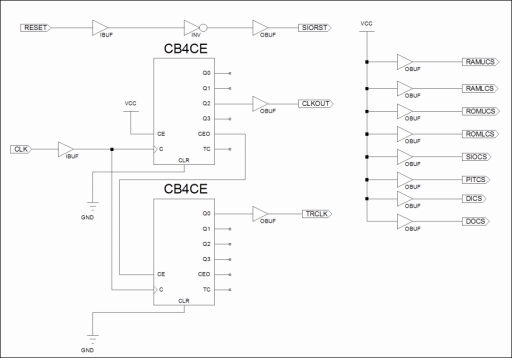

既に基板に実装されているRAMやペリフェラルがバスに対して変にアクティブにならないように全チップセレクトをディセーブル、リセットと分周されたクロックは出力されるような仮ロジックをCPLDに書き込みました

これで先ずは82284のリセットとクロック動作が確認できます

早速、デバイスを基板に実装。

電源ONで無事水晶が発振。原振8MHzとCPLDの分周出力1MHz,250kHzが得られました。黄色いリセットボタンを押したときのリセット信号もOK、とりあえず82284は生きていたということで一安心です。