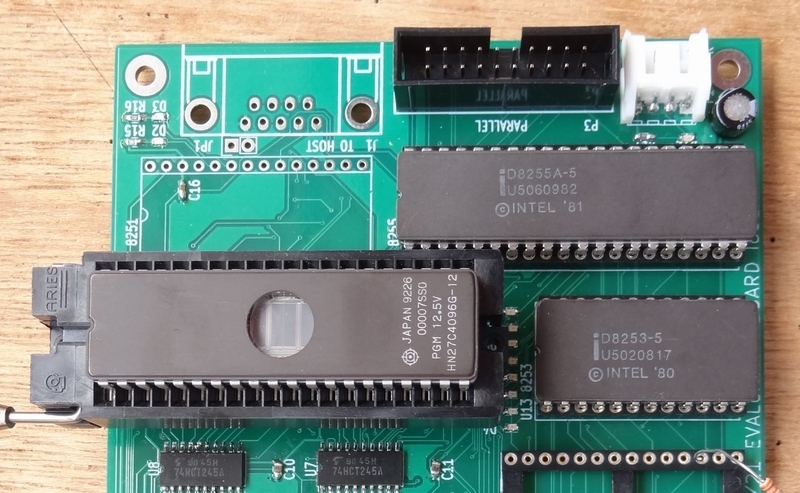

パラレルインターフェース8255に続いてタイマカウンタ8253を実装しました。

ところで今回多用しているCERDIPのICですが、丸ピンICソケットに非常に差しにくいのです。プラスチックDIPだとパッケージ幅とデュアルインラインの幅に多少余裕があって足も開き気味なのでバネを押し縮める要領ではめることができますが、CERDIPはパッケージのほとんど側面から垂直に足が生えていて、特に40ピンの大型のもので、うまくソケットの穴に嵌らないまま押し込むとピンが座屈してしまったりします。ヘタすると金属疲労でポキっといきそう。

高信頼性の丸ピンより、安い板バネソケットの方がかえって差し込みしやすそうです。

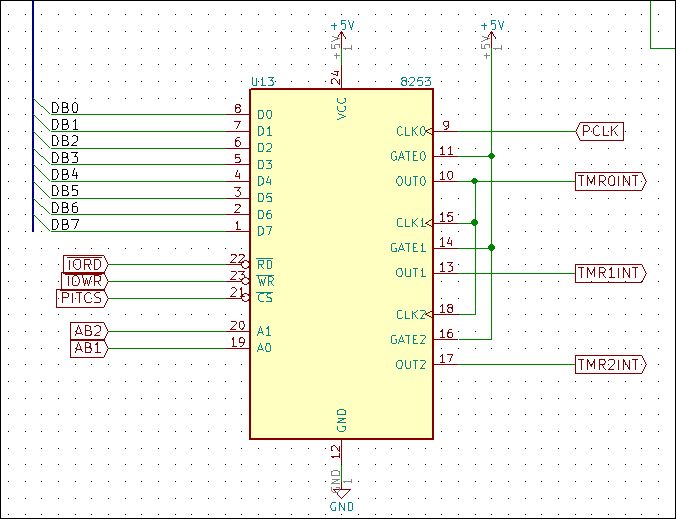

カウンタの配線は以下のようになっています。

PCLKはクロックジェネレータ8284で生成される信号で、水晶原振を3分周したCPUクロックをさらに2分周した周辺デバイス用クロックで2.4576MHzになります。

これがカウンタ#0に入力され、その出力はカウンタ#1とカウンタ#2に供給。

それぞれのカウンタ出力は割込みコントローラ8259の割込み要因になります。

カウンタ時定数はプログラム次第ですが

カウンタ#0 時定数=4 分周出力614.4kHz

カウンタ#1 時定数=6144 分周出力100Hz

カウンタ#2 時定数=61440 分周出力10Hz

カウンタ#0 時定数=4 分周出力614.4kHz

カウンタ#1 時定数=6144 分周出力100Hz

カウンタ#2 時定数=61440 分周出力10Hz

とするのを想定しています。

何故カウンタ#0出力を614.4kHzにするのか?

何故カウンタ#0出力を614.4kHzにするのか?

それはまた後で・・・